1.10. 芯片烧录接线和供电说明

1.10.1. 支持烧录的芯片最小系统

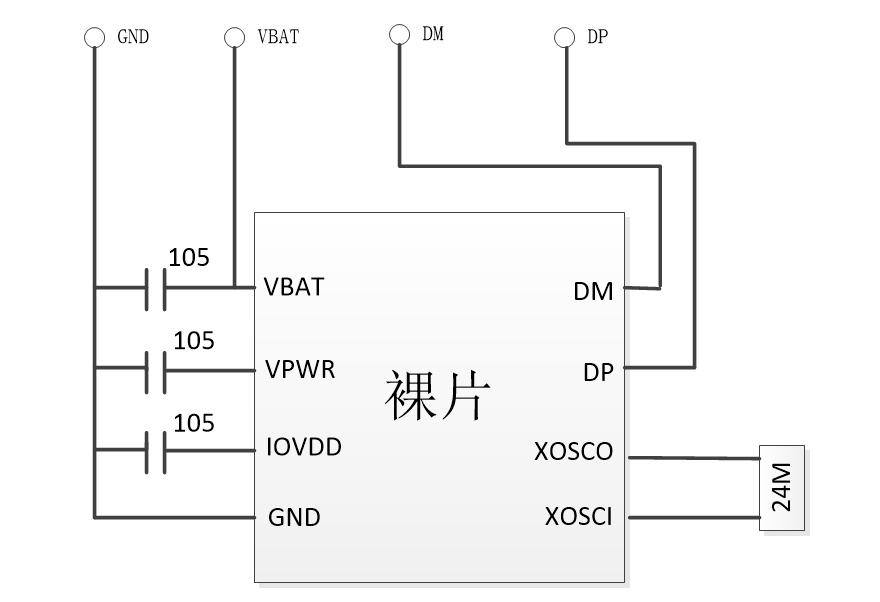

芯片(裸片)的供电引脚焊接105电容到GND,晶振引脚接上24M晶振(免晶振方案不用接晶振),芯片的VBAT、DM、DP、GND引脚(部分芯片无DM,DP为其他引脚),接线到烧录器通道1或通道2排针对应引脚即可实现芯片烧录,如支持烧录的芯片最小系统所示。

支持烧录的芯片最小系统

1.10.2. 烧录通道排针接口定义和接线说明

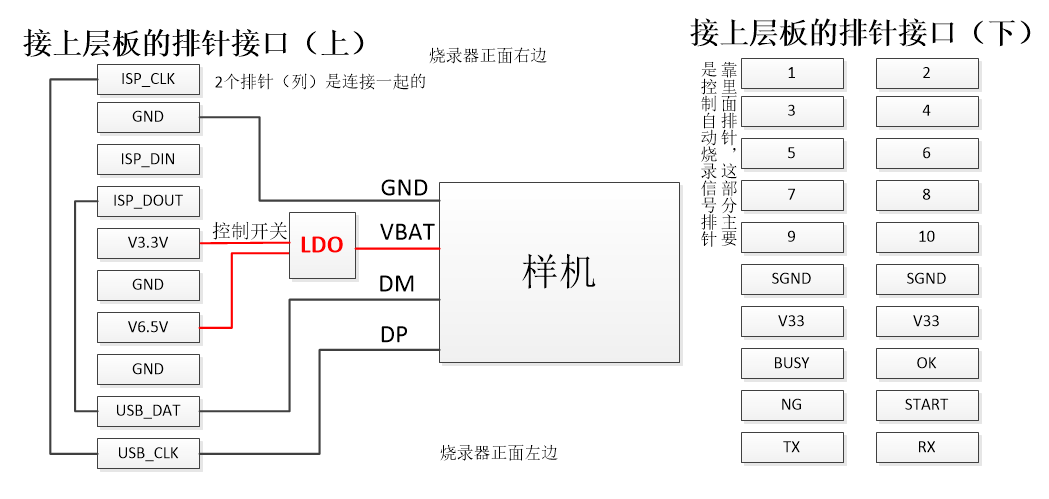

烧录通道1或通道2对应排针接口定义和接线参考图, 如烧录座或样机接线参考图所示。

烧录座或样机接线参考图

使用带LDO电压转换电路方式接线说明

如烧录座或样机接线参考图所示,,烧录座带LDO电压转换电路,即烧录器排针”6.5V”引脚通过LDO硬件电路转为需要的5V,或4.2V等芯片对应的烧录电压,烧录器通过的

3.3V排针引脚控制LDO供电开启和关闭对芯片进行供电控制。烧录器排针引脚和芯片烧录引脚接线关系如下:

烧录器排针 |

芯片引脚 |

|---|---|

6.5V(LDO转换顶板6.5V转5V、4.2V等) |

VBAT |

ISP_DOUT(与USB_DAT连接) |

DM(部分芯片没有DM为其它引脚) |

ISP_CLK(与USB_CLK连接) |

DP(部分芯片没有DP为其它脚) |

GND |

GND |

使用烧录器供电引脚直接输出芯片供电电压方式接线说明

如烧录座或样机接线参考图所示,接线时忽略

LDO部分,烧录器排针”6.5V”直接输出PC工具配置的5V,或4.2V 等芯片对应的烧录电压,烧录器排针引脚和芯片烧录引脚接线关系如下:

烧录器排针 |

芯片引脚 |

|---|---|

6.5V(烧录器直接输出PC工具 |

VBAT |

ISP_DOUT(与USB_DAT连接) |

DM(部分芯片没有DM为其它引脚) |

ISP_CLK(与USB_CLK连接) |

DP(部分芯片没有DP为其它脚) |

GND |

GND |

Note

烧录座带LDO转换电路原因是以前考虑部分未校准的芯片会流到客户手中,导致芯片需要烧录器进行校准;或者部分芯片的efuse存储介质烧录需要6.5V,3.3V等特定电压;

当前的烧录器带有芯片校准检测功能,如果芯片未校准烧录会报错!并且efuse对应的key,lvd等烧录不再需要特定电压;

烧录座可以去掉LDO电路,做成芯片最小系统样式进行烧录!这样烧录座更简单,既可以省物料又可以做成通用烧录座;

使用LDO转换电路给芯片供电也有它的优势,走线短,电源相对更加稳定,烧录通过率可能更高;

1.10.3. 芯片烧录供电说明

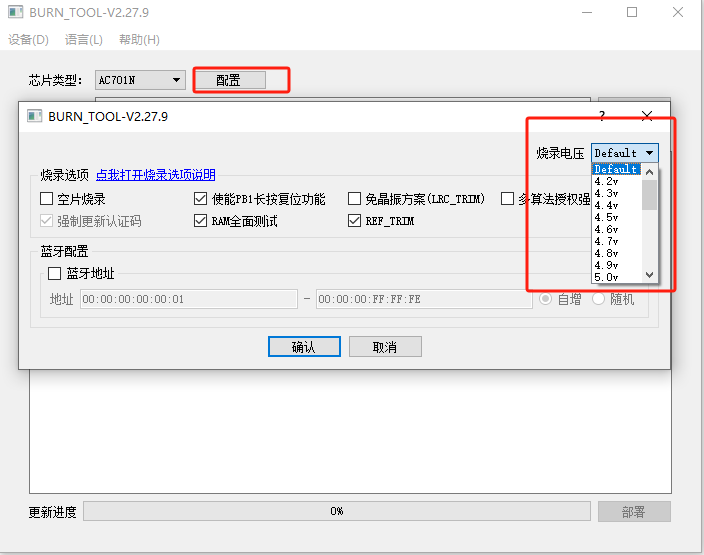

一拖二烧录器V2.27.9及以上固件版本支持烧录座供电电压“4.2V~6.8V”PC工具可配置,主要有如下3种应用情况。

无ldo电路即烧录器排针”6.5V”直接输出PC工具配置的5V,或4.2V等电压到芯片VBAT供电端。

带ldo电压转换电路即通过硬件电路把烧录器排针的6.5V电压转换为芯片需要的供电电压5V,或4.2V等,需配置供电电压为“Default”。

低电烧录供电如IOVDD和VBAT绑在一起的情况,VBAT可以直接到烧录器上排针的3.3V引脚,或通过烧录器排针的6.5V电压转换为芯片需要的供电电压。

烧录电压配置界面如下图所示:

烧录电压PC工具可配置

Note

如果默认配置“4.2V”供电;烧录时如果座子带LDO电路请记得供电电压要配置回 “default”,否则可能因为供电不足导致出现各种烧录问题!

不能直接配置“default”供电电压,烧录不带LDO电路的样机芯片,否则可能因为供电电压过高导致烧坏芯片!

1.10.4. DM,DP引脚样机芯片烧录接线

带DM,DP引脚的芯片通用烧录接线说明

烧录器排针 |

芯片引脚 |

|---|---|

6.5V(烧录器直接输出PC工具 |

VBAT |

ISP_DOUT(与USB_DAT连接) |

DM(部分芯片没有DM为其它引脚) |

ISP_CLK(与USB_CLK连接) |

DP(部分芯片没有DP为其它脚) |

GND |

GND |

带DM,DP引脚的芯片特殊烧录接线说明

AD14N,AC104N,AD23N,AD24N样机芯片烧录接线

烧录器排针 |

芯片引脚 |

|---|---|

6.5V(烧录器直接输出PC工具 |

VBAT |

ISP_DOUT(与USB_CLK连接) |

DM |

ISP_CLK(与USB_DAT连接) |

DP |

GND |

GND |

AC690X样机芯片烧录接线

烧录器排针 |

芯片引脚 |

|---|---|

6.5V(烧录器直接输出PC工具 |

VBAT |

ISP_DOUT(与USB_DAT连接) |

DM |

ISP_DIN(与USB_CLK连接) |

DP |

ISP_CLK |

PA3 |

GND |

GND |

1.10.5. 无DM,DP引脚样机芯片烧录接线

AD15N样机芯片烧录接线

烧录器排针 |

芯片引脚 |

|---|---|

6.5V(烧录器直接输出PC工具 |

VBAT |

ISP_DOUT(与USB_DAT连接) |

PB1 |

ISP_CLK(与USB_CLK连接) |

PB0 |

GND |

GND |

AD17N样机芯片烧录接线

烧录器排针 |

芯片引脚 |

|---|---|

6.5V(烧录器直接输出PC工具 |

VBAT |

ISP_DOUT(与USB_DAT连接) |

PA9 |

ISP_CLK(与USB_CLK连接) |

PA8 |

GND |

GND |

AD21N、AC75N样机芯片烧录接线

烧录器排针 |

芯片引脚 |

|---|---|

6.5V(烧录器直接输出PC工具 |

VBAT |

ISP_DOUT(与USB_DAT连接) |

PC3 |

ISP_CLK(与USB_CLK连接) |

PC2 |

GND |

GND |

AC704N、AC705N、AC680N、AC110N,AC111N,AC112N样机芯片烧录接线

烧录器排针 |

芯片引脚 |

|---|---|

6.5V(烧录器直接输出PC工具 |

VBAT |

ISP_DOUT(与USB_DAT连接) |

VPWR |

ISP_CLK(与USB_CLK连接) |

PA02 |

GND |

GND |

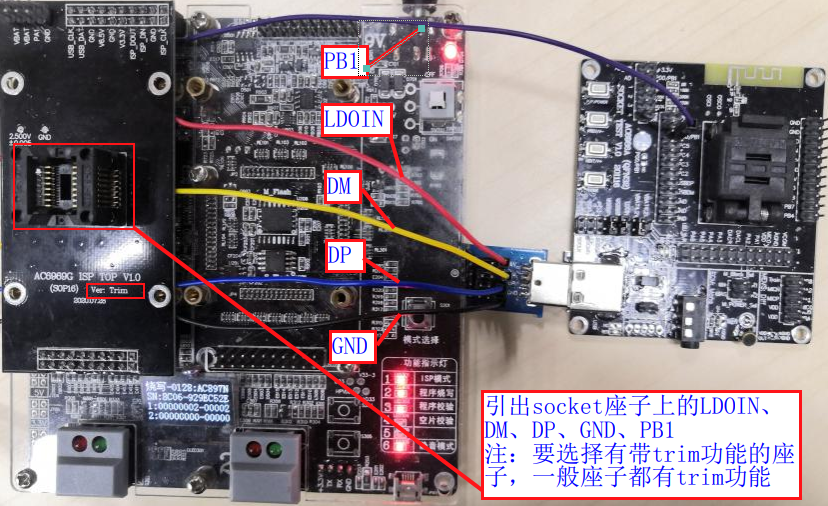

1.10.6. 样机芯片校准接线

此种接线方式可对样机、DEMO板、开发板上的芯片进行烧录测试,也可对芯片进行校准。

简便的方法是找一个SOP封装的上层板(容易引线),引出socket座上的VBAT(或LDOIN/VPWR)、DM、DP、GND,PB1 2.5V基准源,

接到样机芯片对应引脚上,如校准样机芯片接线所示。走正常烧录流程即可实现芯片校准、程序烧录。

校准样机芯片接线

Note

部分芯片上层板的2.5V基准源并不一定是接PB1,视具体硬件设计而定;

部分芯片校准电源供电接的是VBAT,而不是LDOIN/VPWR引脚;

量产芯片,芯片出厂已经校准;只有出现ADC模块,VBAT充电模块等精度不够的情况才会在烧录阶段再次校准;