7.37. 系统各模块时钟介绍

Overview

介绍系统的时钟结构

7.37.1. 时钟类型

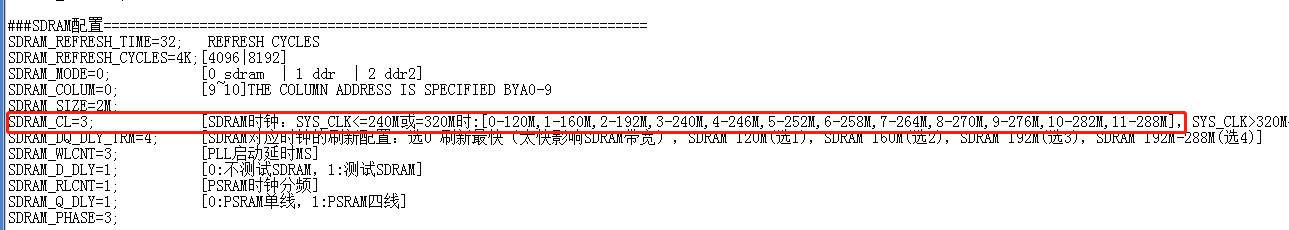

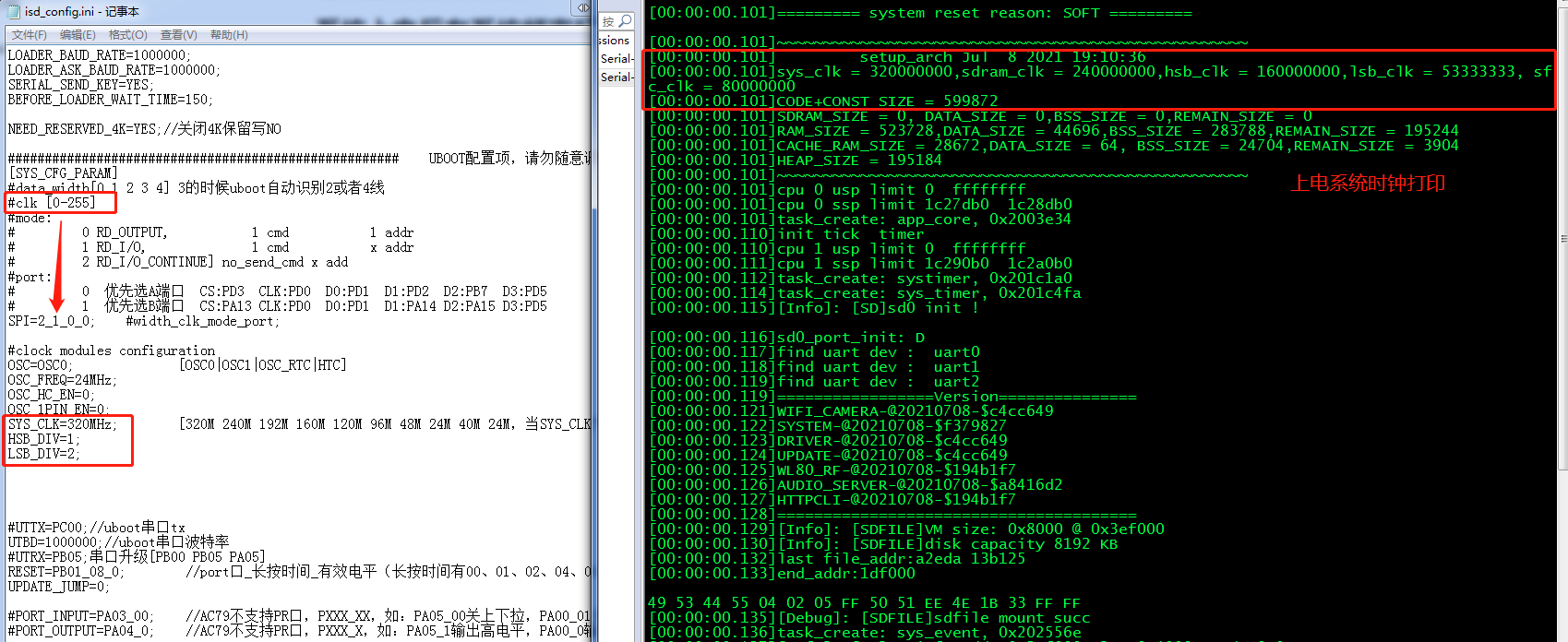

sys_clk:系统时钟,可以在对应CPU目录下(如:cpu/wl82/tools)的isd_config_rule.c文件中SYS_CLK=320MHz;修改配置sdram_clk:sdram时钟,当芯片不带sdram,则该时钟为0,可以在对应CPU目录下(如:cpu/wl82/tools)的isd_config_rule.c文件中SDRAM_CL=3;修改配置hsb_clk:高速时钟(系统时钟分频),可以在对应CPU目录下(如:cpu/wl82/tools)的isd_config_rule.c文件中HSB_DIV=1;修改配置lsb_clk:低速时钟(高速时钟分频),可以在对应CPU目录下(如:cpu/wl82/tools)的isd_config_rule.c文件中LSB_DIV=2;修改配置sfc_clk:flash时钟(高速时钟分频,正常跑系统时从flash读取程序的时钟),可以在对应CPU目录下(如:cpu/wl82/tools)的isd_config_rule.c文件中[SYS_CFG_PARAM]的#clk [0-255]修改配置,如sfc_clk分频系数为2:SPI=2_1_0_0; sfc_clk分频系数为4:SPI=2_3_0_0;

Note

上述的hsb_clk、lsb_clk、sfc_clk的配置项是对应时钟分频系数,计算方法为:时钟/(分频系数+1),写0则没有分频(即1分频),1则为2个分频。 注意事项:一般系统:sys_clk为160M-320M,hsb_clk应为80M-160M,lsb_clk应为30M-60M,sfc_clk应为60M-80M,时钟越低越有助于降低系统功耗。

7.37.2. 高低速(HSB/LSB)时钟硬件模块

AC790x型号

高速时钟硬件模块:SFC、SDRAM、PSRAM、AES、DCP、JPEG、ISC。 低速时钟硬件模块:USB、SD、SPI、IIC、PAP、TIME、PWM、ADC、DAC、UART、SHA、RDEC、IR、CTMU、PLINK、ALINK、AUDIO、ENC、SBC、SRC、WIFI、BT、DMA_COPY、EQ等。

AC791x型号

高速时钟硬件模块:SFC、SDRAM、PSRAM、AES、DCP、JPEG、ISC、IMD、EMI。 低速时钟硬件模块:USB、SD、SPI、IIC、PAP、EMI、TIME、PWM、ADC、DAC、UART、SHA、RDEC、IR、CTMU、PLINK、ALINK、AUDIO、ENC、SBC、SRC、WIFI、BT、DMA_COPY、EQ等。

Important

通过对芯片进行温度范围-40℃到80℃测试,探测芯片最高稳定运行频率,得到如下测试结论:

①默认推荐系统频率320MHz和SDRAM频率192MHz;

②若有更高性能要求,系统频率可设为396MHz,和SDRAM频率可设为240MHz(由于内封SDRAM有些不支持,生产会导致较多不良率),和内核电压档位设为最高挡位1.38V。

当需要系统时钟为396M:修改配置为 SYS_CLK=396MHz;

sdram时钟配置在 isd_config_rule.c 文件中 SDRAM_PLL3_EN=0; 和 SDRAM_PLL3_NOUSB_EN=0; 选项,注意:两个选项只能开启其中1个。

当开启 SDRAM_PLL3_EN=1; 则sdram强制为240M,SDK程序 允许使用硬件USB2.0接口。

当开启 SDRAM_PLL3_NOUSB_EN=1; ,则sdram跟随 SDRAM_CL=2 的选项选择对应时钟,此时 ``SDRAM_DQ_DLY_TRM=3;``也需要更改对应值,SDK程序 禁止使用硬件USB2.0接口。

注意:系统时钟>320MM,则高速时钟分频系数为2,即``HSB_DIV=2;``,否则系统可能出现无法正常运行,特别是系统时钟>=360M。。

③若客户系统频率配置超过396MHz或者SDRAM频率配置超过192MHz,存在极大的风险,生产上必然会有不良芯片;