7.3. CPU性能测试

Overview

本示例展示了CPU性能指标的测试

7.3.1. DEMO

使用工程:示例代码见 apps/common/example/third_party/BenchMark/main.c ,测试时需要在 apps/demo/demo_hello 添加相应代码。

7.3.2. 示例说明

在嵌入式处理器领域最为知名和常见测试CPU性能的就是:Dhrystone 和 CoreMark。

CoreMark是由EEMBC(Embedded Microprocessor Benchmark Consortium)的Shay Gla-On于2009年提出的一项基准测试程序,CoreMark的主要目标是简化操作,并提供一套测试单核处理器核心的方法。测试标准是在配置参数的组合下单位时间内运行的CoreMark程序次数(单位:CoreMark/MHz),该数字值越大则说明测试的性能越好。 Dhrystone的重要性在于其能作为处理器整数计算性能的指标, 与Coremark不同的是,Dhrystone的主要部分实际上暴露了编译器优化工作负载的能力,而不是实际MCU或CPU的能力的性能;

DMIPS: Dhrystone MIPS,并非字面上每秒百万条指令的意思。它是一个测量CPU运行一个叫Dhrystone(整数运算)的测试程序时表现出来的相对性能高低的一个单位(很多场合人们也习惯用MIPS作为这个性能指标的单位);

Dhrystone: 是于1984年由Reinhold P. Weicker设计的一套综合的基准程序,该程序用来测试CPU(整数)计算性能。其名“Dhrystone”是与另一算法“Whetsone”区分而设计的名字。与Whetsone不同,Dhrystone并不包括浮点运算,其输出结果为每秒钟运行Dhrystone的次数,即每秒钟迭代主循环的次数;

Linpack测试系统浮点性能;

pi_css5_src 测试CPU的浮点运算能力,测试CPU计算特定位数圆周率所需的时间;

whetstone测试浮点运算效率和速度;

STM32F4和ESP32芯片在 eembc官网 分数对比

7.3.3. 示例流程

c_main()入口创建

BenchMark_test_task任务

BenchMark_test_task函数流程测试

coremark测试

dhrystone测试

Linpack测试

whetstone测试

pi_css5_src

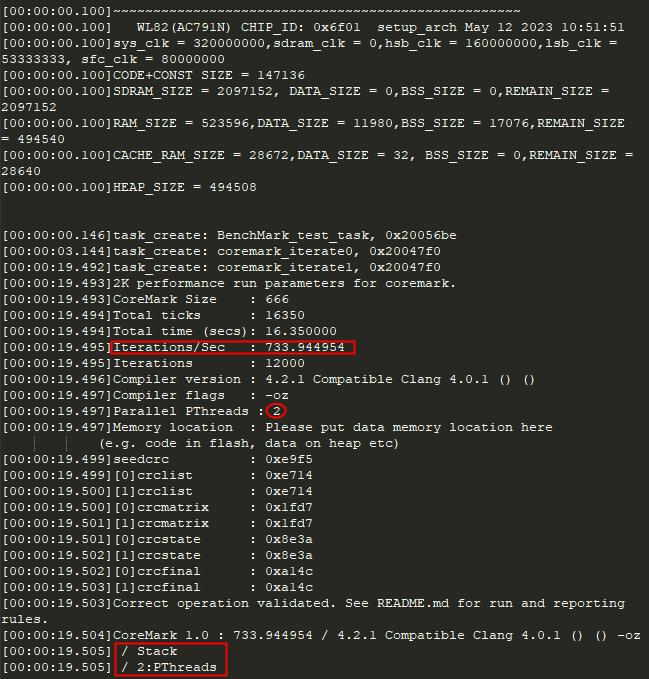

- 跑SFC无SDRAM, CPU时钟320M, SDRAM时钟192M,SFC时钟80M, flash 2线模式的coremark双核测试结果:

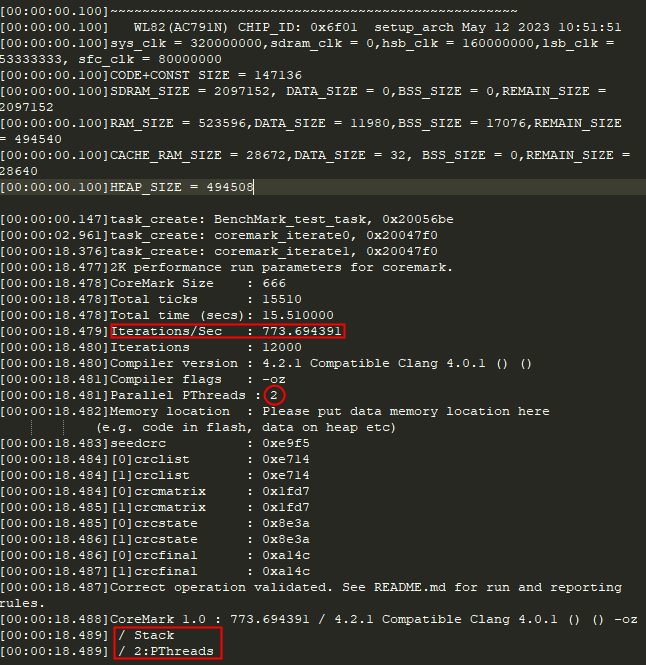

- 跑SFC有SDRAM, CPU时钟320M, SDRAM时钟192M,SFC时钟80M, flash 2线模式的coremark双核测试结果:

- 跑SDRAM, CPU时钟320M, SDRAM时钟192M, SFC时钟80M, flash 2线模式的coremark双核测试结果:

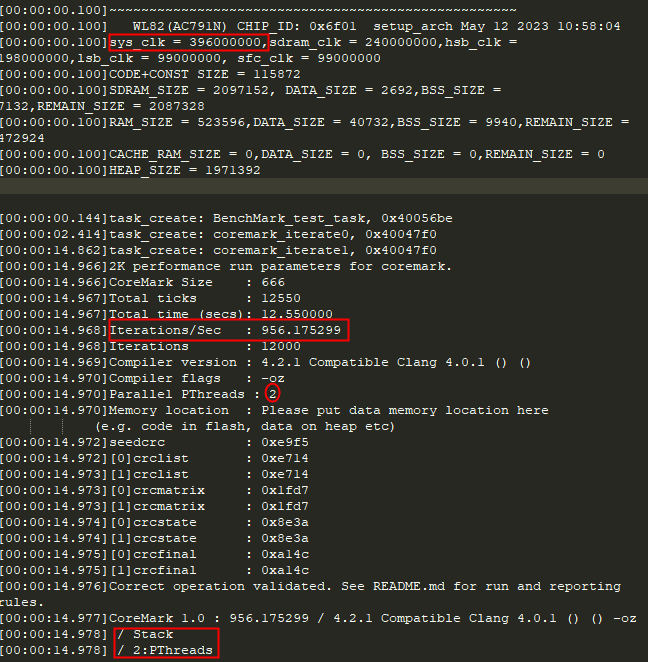

- [超频测试,不可取] 跑SDRAM, CPU时钟396M, SDRAM时钟240M, SFC时钟99M, flash 2线模式的coremark双核测试结果:

7.3.4. 常见问题

AC791N CoreMark/MHz 基本在2.41的水平;

通常影响CPU性能测试结果的因素有:

代码运行在内部ram,sdram,flash会依次降低cpu性能;

flash时钟,双/四线,sdram时钟,系统时钟影响cpu性能;

由于硬件只支持单精度浮点指令, 因此双精度浮点影响cpu性能