7.36. SDRAM配置

Overview

介绍sdram的常规配置

7.36.1. SDRAM使能以及SDRAM大小配置

芯片封装不带sdram时,在SDK主工程cbp文件或者主工程Makefile加上宏定义

CONFIG_NO_SDRAM_ENABLE。芯片封装带有sdram时,在SDK主工程cbp文件或者主工程Makefile去掉宏定义

CONFIG_NO_SDRAM_ENABLE,并在board_config.h中修改__SDRAM_SIZE__,请根据实际内存修改。

Note

芯片不带sdram,去掉宏定义 ``CONFIG_NO_SDRAM_ENABLE``打开sdram,则会跑不起,当实际封装的sdram大小为8M却配置__SDRAM_SIZE__=2M,则系统正常运行后,程序使用超过2M大小地址会出现异常死机等现象。

7.36.2. SDRAM时钟配置

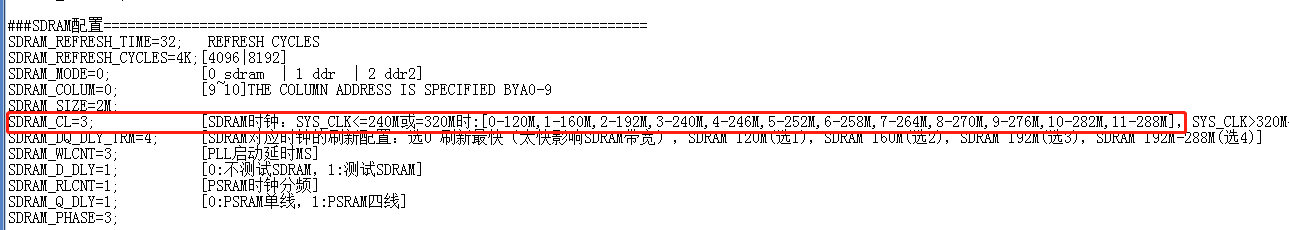

sdram时钟在可以在对应CPU目录下的 isd_config_rule.c 文件中 SDRAM_CL=3; 修改时钟配置

sdram时钟应根据系统时钟来配置,SYS_CLK<=240M或=320M时:[0-120M,1-160M,2-192M,3-240M,4-246M,5-252M,6-258M,7-264M,8-270M,9-276M,10-282M,11-288M],详见下图。

Note

sdram时钟尽量<=192M,大于192M以上时钟sdram稳定性性不高,特别是240M以上,温度漂移对sdram稳定性影响较大。 一般情况下SDK默认192M,用户只能减小sdram时钟,不能随意增大,建议使用默认即可。

①

isd_config_rule.c文件中SDRAM_PLL3_NOUSB_EN和SDRAM_PLL3_EN选项全配置0。 当系统时钟SYS_CLK>320M并且 < 384M时:SDRAM时钟为SYS_CLK*1.5/2,SYS_CLK >= 384M时:SDRAM时钟为SYS_CLK/2。 当系统时钟SYS_CLK>240M并且 < 320M时:SDRAM时钟为SYS_CLK*1.5/2;SDRAM时钟为SYS_CLK/2或SYS_CLK*1.5/2,此时SDRAM_CL=2更改无效。 系统时钟配置详情 < 系统各模块时钟介绍 >。②

isd_config_rule.c文件中SDRAM_PLL3_NOUSB_EN和SDRAM_PLL3_EN选项其中一个为1。 此时系统时钟:任意值(120M-396M),sdram时钟固定在240M、192M、160M、120M等时钟。如:当需要系统时钟为396M:修改配置为

SYS_CLK=396MHz;。 sdram时钟配置在isd_config_rule.c文件中SDRAM_PLL3_EN=0;和SDRAM_PLL3_NOUSB_EN=0;选项,注意:两个选项只能开启其中1个。 当开启SDRAM_PLL3_EN=1;则sdram强制为240M,SDK程序 允许使用硬件USB2.0接口,当开启SDRAM_PLL3_NOUSB_EN=1;, 则sdram跟随SDRAM_CL=2;的选项选择对应时钟,此时SDRAM_DQ_DLY_TRM=3;也需要更改对应值,SDK程序 禁止使用硬件USB2.0接口。注意:系统时钟>320M,则高速时钟分频系数为2,即

HSB_DIV=2;,否则系统可能出现无法正常运行,特别是系统时钟>=360M。